Hello Gentlemen,

This is my first post on this forum, so if the information which I’m supplying is not sufficient, please let me know.

Currently I’m working a custom implementation of the DW1000. This implemenation is currently in the testing phase and sadly I ran into some trouble.

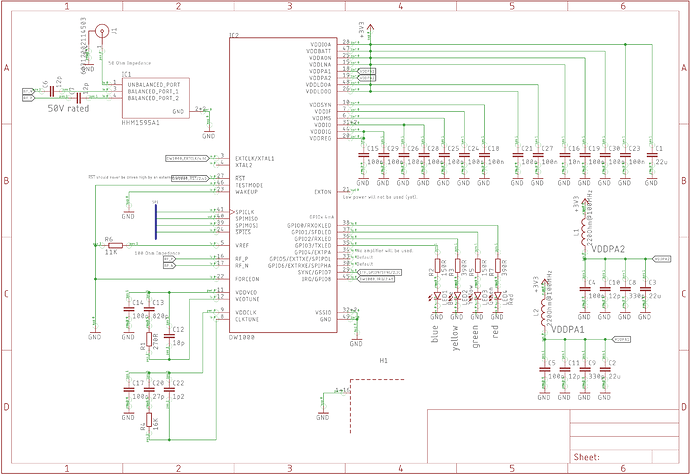

For the custom design I followed a lot of the design guides (which are very helpful). To make sure that the assembly of the PCB would remain within budget I designed it with mainly 0402 components and the PCB to be manufactured at JLCPCB. The external clock of the DW1000 is supplied by an external clock generator.

After manual assembly of two prototypes it was discovered that the DW1000 communicates with the MCU as expected and is mostly operating properly. The part which is not working is (presumably) the matching of the antenna.

Up to this point I’ve had zero communication with any external devices. The DWM1001 is used to send and receive messages. Why the messages are not being received or transmitted by the custom design is unclear. For testing I used two antennas:

-

WB002 of the DecaWave reference design

-

Taoglass Limited FXUWB10.01.0100C

Both antennas don’t work, very likely due to bad impedance matching on the PCB. This is where I’m not sure. During the design phase I’ve put quite some emphasise on the correct matching of the RF traces. I use a four layer PCB, with the RF traces matched with the internal ground plane as a reference.

Sadly I have no VNA to test the traces at the UWB frequencies, so I’m very much in the dark right now.

By this post I hope that someone might be able to spot the problem in my design. Due to the 0402 components it certainly ain’t perfect, but I don’t see why it wouldn’t work.

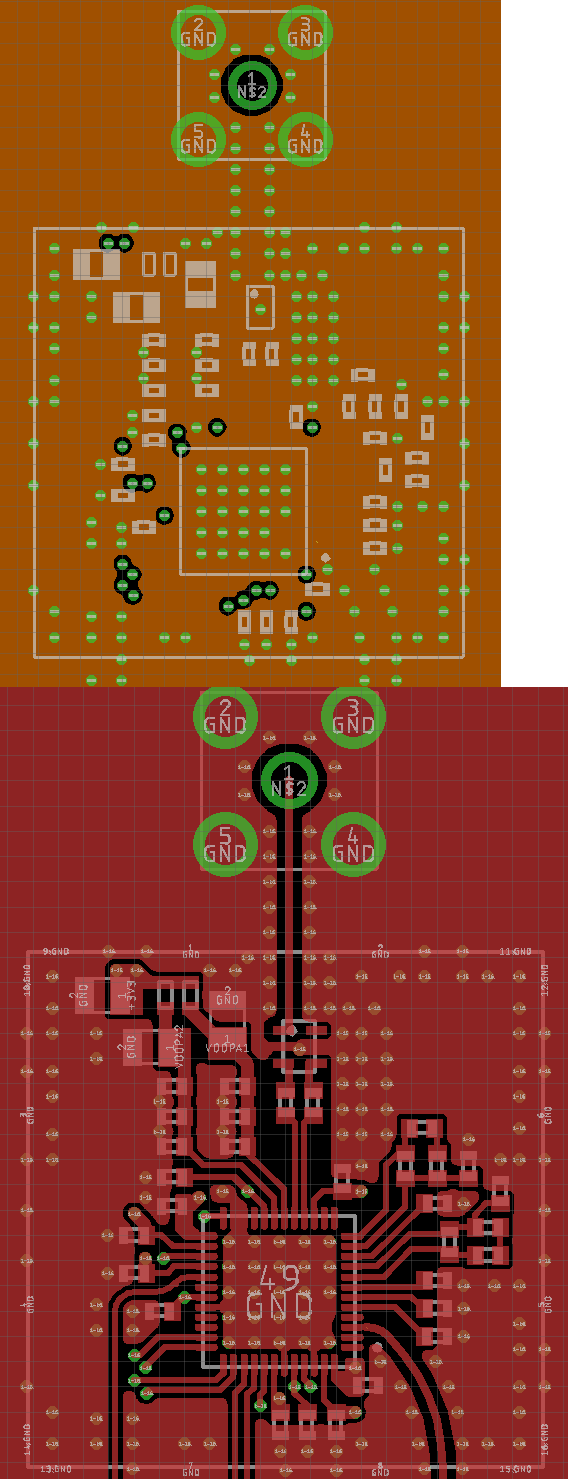

Here you can see the board layout with the solid ground plane right below it as the reference:

The width of the 100 ohm differential traces is 0.2mm, the width of the 50 ohm trace to the SMA connector is 0.293mm (11.55mil). The traces are 7.1mill above the internal ground plane.

Hopefully I’ve now supplied a sufficient amount of information for someone to spot the problem.

It’ll be very much appreciated!

Thank you,

Glen