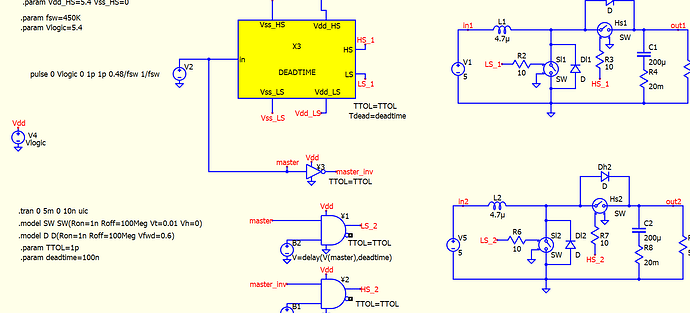

Change your input pulse source rise time and fall time from 10ns to 1ps (both rise and fall to 1ps).

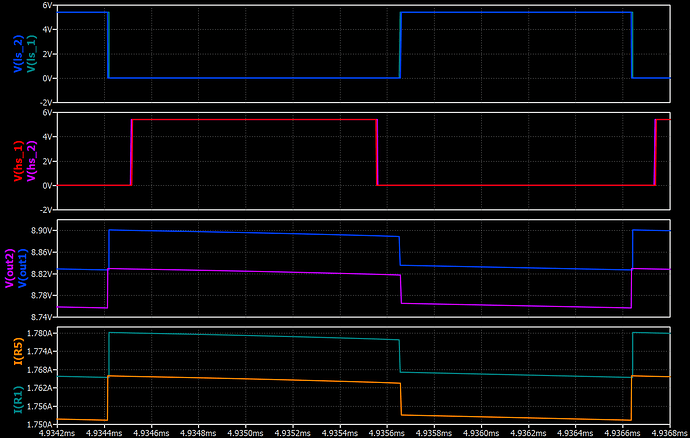

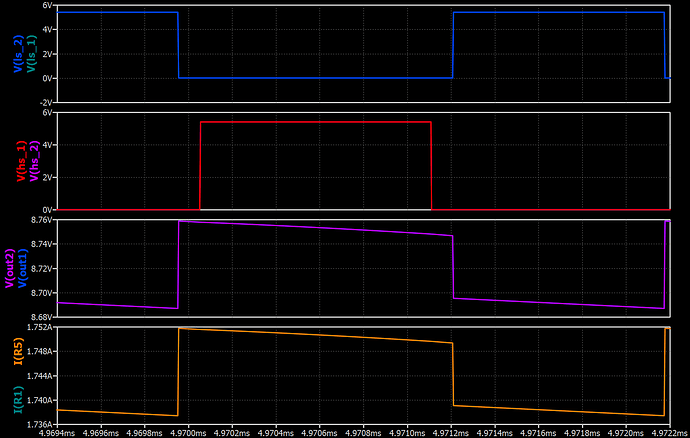

Compare if you can still see this different. Input logic reference threshold are different in these two gate driver circuits.

@KSKelvin but rise time and fall time of 1ps its very fast…in reality I think will be of tents of ns (10ns, 20ns, etc).

And what to do when the control of that rise time and fall time of V2 pulse will not be possible?

It is strange that the two results can be matched only by that very fast rise time and fast time …and why is so…

Nothing strange… when logic goes high and low relates to where the logic threshold is. This 10ns rise and fall time affect when logic output change as these two circuits with different logic threshold. I think if you consider the logic interface with input signal to have exactly the same logic threshold (i.e. same value for Vss+REF), you can have same timing in both circuits.

You have to think where the different lies in the circuit implementation.

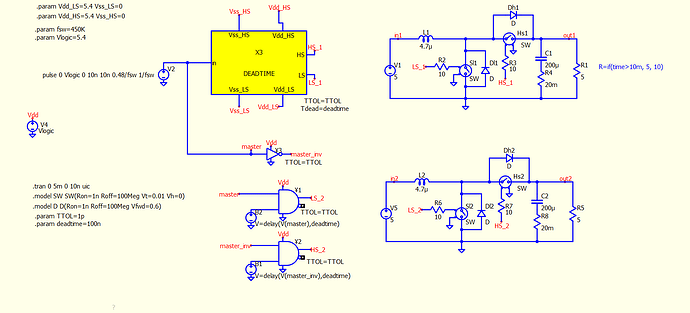

In comparing these two circuits, what I did is that to put two circuit (not symbol) into one schematic and not using an embedded symbol. If you keep your embedded symbol, you have no way to probe the timing or change parameters of that circuit and identify where is the different.

Refer to this post, if you have different logic threshold, you got different timing for a signal with rise and fall time.

Actually, 10us rise/fall time just introduce very small timing different, but as you are asking why, then you have to go back to this fundamental concept.